**IJCRT.ORG**

ISSN: 2320-2882

# INTERNATIONAL JOURNAL OF CREATIVE RESEARCH THOUGHTS (IJCRT)

An International Open Access, Peer-reviewed, Refereed Journal

# DESIGN OF BANDGAP VOLTAGE REFERENCE CIRCUIT WITH LOW TC AND HIGH PSRR IN 180nm CMOS TECHNOLOGY

Mr Arkala Theja<sup>1</sup>, Surigi Anusha<sup>2</sup>, Samineni Bhavya<sup>3</sup>, Syed Zuber<sup>4</sup>

Associate Professor<sup>1</sup>, UG Students<sup>2, 3, 4</sup>

I. Department of Electronics and Communication Engineering TKR College of Engineering and Technology, Hyderabad, India.

Abstract: In this paper a low power, high precision bandgap reference is proposed and analyzed. The voltage reference is obtained by summing a proportional-to-absolute-temperature (PTAT) voltage and a complementary-to-absolute-temperature (CTAT) voltage. In this paper CTAT voltage is obtained from conventional circuit i.e.; based on a scaled emitter-base voltage of a BJT and PTAT voltage is obtained by using current mirror structure and as well as by using operational amplifier. The designed circuit was implemented using Cadence Virtuoso in CMOS 180nm process technology. A new low temperature coefficient (TC) high power supply rejection ratio (PSRR) bandgap voltage reference is presented in CMOS technology. In order to achieve low TC and high PSRR voltage reference with small area overhead and good practicability, the proposed circuit uses a curvature correction method based on sub-threshold current and a PSRR enhancement circuit. When the power supply voltage is 1.8V, this circuit is devised and verified using 0.18um CMOS process. The results show the output voltage is constant at 1.2V at room temperature. The TC is 6.1ppm/°C in a wide temperature range of -40°C to 125°C. The measured PSRR is -70dB.

Keywords: CTAT, PTAT, TC, PSRR

# I. INTRODUCTION

In these modern days, the Integrated Circuits are being designed to achieve higher integration and higher performance. While in modern electronics, digital technology has get to be the development trend, a part from this, analog circuits still play an incomparable role. The signals generated by most electronic devices are analog. These signals must be processed before digital processing and after digital processing; the signal must be converted into analog at the output. The research on analog IC design using CMOS technology becomes very important since the CMOS technology has been widely used. I proposed to design a very efficient bandgap reference. Bandgap reference circuit is a circuit designed to produce a stable and precise output reference voltage which is independent of variations in Process, Temperature and Voltage.

# II. INTRODUCTION TO CADENCE

The software tool used to construct the bandgap reference circuit is cadence virtuoso. The Cadence virtuoso system platform design is a holistic, system-based solution and it provides the functionality to drive simulation and LVS-clean layout of integrated circuits and packages from single schematic. There are two main functionalities of cadence virtuoso, they are implementation and analysis.

The implementation flow is used to create an Integrated circuit package schematic in virtuoso schematic editor and it transfer the whole schematic data to cadence Sip layout to layout the physical design. In addition, this flow offers the capability to generate and verify library parts, output a bill of materials (BOM), and perform layout versus schematic (LVS) checking.

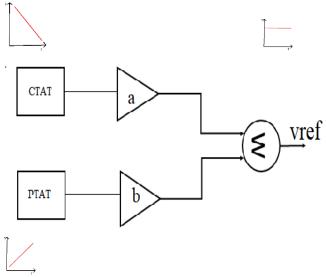

# **BLOCK DIAGRAM**

Figure.1 Block diagram of BGR circuit

#### IV. DESIGN OF CTAT

The CTAT is traditionally generated from a diode (or) diode-connected BJT. The diode voltage drop across the base-emitter junction, V<sub>BE</sub> of a BJT changes complementary to absolute temperature (CTAT). The I-V relationship for a bipolar junction transistor can be

$$I_{\rm C} = I_{\rm S} e^{\frac{\rm V_{\rm BE}}{N \rm V_{\rm T}}}$$

$V_{\rm BE}$  is the base-emitter voltage of a diode or a diode-connected bipolar transistor,  $I_{\rm C}$  is the collector current,  $I_{\rm S}$  is the saturation current, N is the non-ideality factor and VT is the thermal voltage. The above equation can be rearranged as

$$V_{\rm BE} = NV_{\rm T} ln(\frac{I_{\rm C}}{I_{\rm S}}),$$

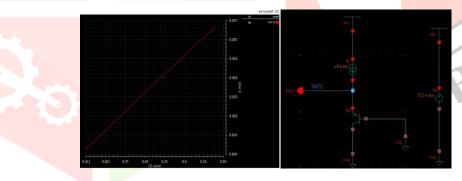

Where the current IS which is CTAT in nature, more dominant than threshold voltage. Hence, the resultant voltage becomes CTAT. Figure 2 illustrates the implementation of CTAT circuit with experimental results in which the CTAT voltage decreases with a range of slope of -1.7 to -2.05mv/□c.

Fig. 2. CTAT circuit with experimental results

#### III. DESIGN OF PTAT

When two BJTs are operated with unequal current densities and areas, then the difference in the base-emitter voltages,  $\Delta V_{BE}$  of the transistors is proportional to absolute temperature (PTAT). The PTAT is given as

$$V_{BE} = V_T \ln (n)$$

Where,

$$\Delta V_{BE} = V_{BE1} - V_{BE2} = V_T \ln(n)$$

and  $V_T = kT/q$

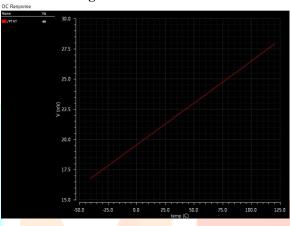

Where k is Boltzmann's constant, T is the absolute temperature; q is the electron charge, of the two BJTs, respectively. In above equation, the voltage difference in the base emitter voltages of transistors is directly proportional to the threshold voltage, i.e. directly proportional to the temperature. The experimental results of PTAT are illustrated in Figure 3 and figure 4.

Figure 3. PTAT circuit

Figure 4. Experimental results of PTAT

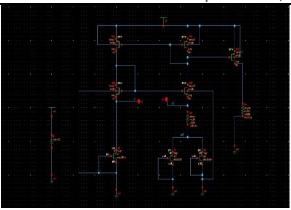

#### IV. DESIGN OF BANDGAP REFERENCE

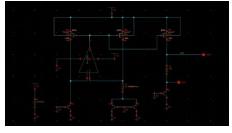

BGR circuit is combinational of CTAT circuit and PTAT circuit. The output voltage of this circuit is constant with respect to temperature. This BGR circuit produces a constant output voltage with respect to change temperature, pressure. A bandgap core circuit and a start-up circuit are included in this approach. The bandgap core is a PTAT circuit which will be proportionate to absolute temperature and the output circuit acts as a CTAT circuit which means compliment to absolute temperature. The OP-Amp used in this circuit will provide high gain. The circuit diagram of this conventional BGR.

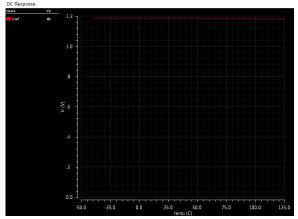

BGR circuit with constant voltage and current outputs is presented with a 1.2 V supply voltage. The first stage provides a fixed BGR voltage of 1 V with a temperature coefficient (TC) of 6.1 ppm/ 0 C. It includes a 2-stage op-amp for higher power supply rejection ration (PSRR). The op-amp has a closed feedback loop to neglect the current proportional-to-absolute-temperature (PTAT) and the negative TC. The second stage provides a higher current gain and an enhanced PSRR. It produces a fixed BGR current of 100  $\mu$ A. Simulation results including PVT variations and Monte Carlo analysis have been performed, in 180 nm CMOS technology, to the proposed design which achieves a chip area of 0.03 mm 2, a higher temperature range of-40~125 0 C, a 35 ppm/ 0 C TC, a-70 dB PSRR .

Figure.5 Proposed bandgap reference circuit

This circuit is designed and simulated by using cadence virtuoso. The experimental results are illustrated in Figure.6.

Figure 6. Experimental results of proposed BGR.

# VII. CONCLUSION

Based on the standard 0.18nm CMOS technology devised a low TC and high PSRR bandgap voltage reference in this review. The circuit shows great in general execution by performing the temperature characteristic at high temperature and adding PSRR to enhance the circuit. The improved BGR proposed in this paper have the benefits of low power utilization, little region and basic devise technique, circuit is reasonable for all CMOS technology. From the simulation results, the temperature coefficient is simply 6.1 ppm/°C in the scope of - 40°C to 125°C, the low-frequency power supply rejection proportion is – 70 dB.

|                         | This design        | [1]             | [2]                | [3]                    |

|-------------------------|--------------------|-----------------|--------------------|------------------------|

| Process                 | 0.18µ<br>m<br>CMOS | 0.5μmBiCMO<br>S | 0.35µ<br>m<br>CMOS | 0.13<br>µm<br>CMO<br>S |

| Temperatur<br>e         | -40 to<br>125      | -40 to 125      | -15 to<br>150      | -55<br>to125           |

| Supply                  | 1.8                | 5               | 2.5                | 1.2                    |

| Reference<br>voltage(V) | 1.2                | 1.264           | 0.6177             | 0.3                    |

| TC<br>(ppm/°C)          | 6.1                | 8.9             | 3.9                | 65                     |

| PSRR<br>(dB)            | -70                | -73             |                    | -109                   |

**Table-1 Performance comparison**

# VIII. REFERENCES

- [1] F. Wu, H. Deng and Y. Yin, "A high PSRR bandgap reference for LED driver," 2016 IEEE Information Technology, Networking, Electronic and Automation Control Conference, Chongqing, pp. 742-74, 2016.

- [2] D. Colombo, G. Wirth, S. Bampi, F. Nabki and C. Fayomi, "Curvature correction method based on subthreshold currents for bandgap voltage references," IEEE LASCAS), pp. 1-4,2012.

- [3] I. Lee, G. Kim and W. Kim, "Exponential curvature-compensated Bi CMOS bandgap references," in IEEE Journal of Solid-State Circuits, pp. 1396-1403, vol. 29, no. 11.

- [4] C. M. Andreou, S. Koudounas and J. Georgiou, A novel wide temperature- range, 3.9 ppm/°C CMOS bandgap reference circuit. IEEE J. Solid-State Circuits, 47(2): 574-581,2012.

- [5] K. Souri, H. Shamsi, S. Samadian and H. Mirzaie, "A 109dB PSRR, 31|iW folly-MOSFET bandgap voltage reference in 0.13pm CMOS technology," 2010 17th IEEE International Conference on Electronics, Circuits and Systems, Athens, pp. 182-185,2010